#### **Standard Products CT1611 Microprocessor Interface** DMA Controller with Buffer Memory, **MIL-STD-1750A** Compatible

www.aeroflex.com

#### September 16, 2003

#### **FEATURES**

- Full Bus Control and RTU Operation

- Low Software Overhead

- Complete BI-Directional Message Buffer

- Memory-Mapped DMA Message Transfers

- Simple Programmable Polling Operation in Bus Controller Mode

- Pin Programmable for both 8 and 16 Bit Microprocessors

- Monolithic construction using linear ASICs

- Processed and screened to MIL-STD-883 specs

- Aeroflex is a Class H & K MIL-PRF-38534 Manufacturer

- MIL-PRF-38534 Compliant Devices Available

#### GENERAL

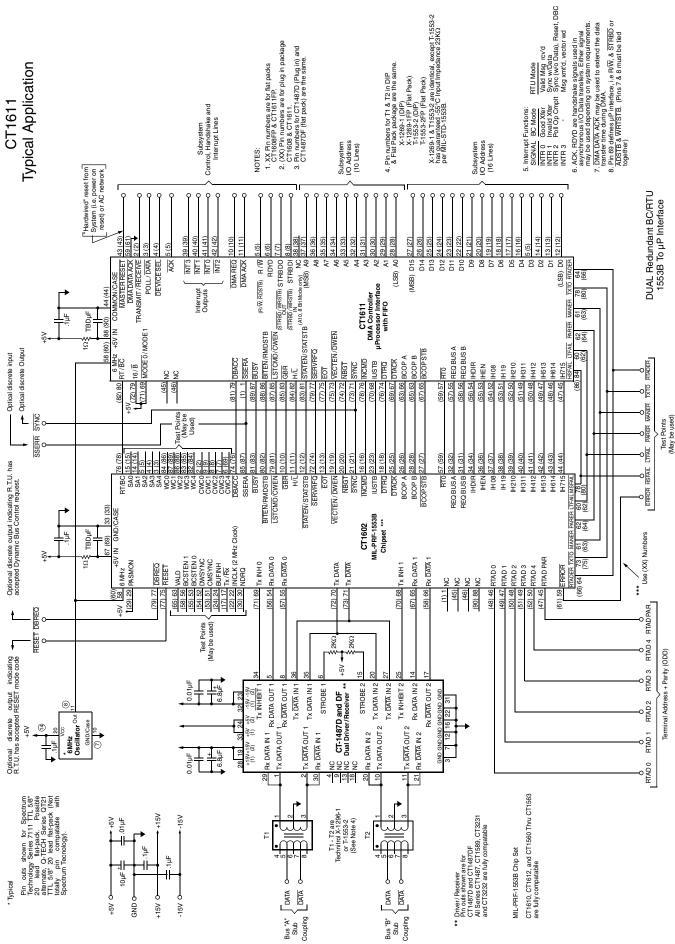

The CT1611 provides a complete Bus Controller and Remote Terminal interface between the MIL-STD-1553B chip set (CT1561, CT1602, CT1610, etc.) and most microprocessor-based systems (F9450A, 68000, 8086, VME bus, Multibus, etc.). The unit is constructed totally with CMOS technology and includes a custom CMOS chip, two HC CMOS FIFO's and HCT CMOS buffers. Thus the interface has extremly low power requirements.

The CT1611 interface permits the use of all 15 mode codes and all types of data transfers as specified in MIL-STD-1553B in both Bus Controller and Remote Terminal operating modes. A Remote Terminal is capable of switching to a Bus Controller when requested via the Dynamic Bus Control mode code.

#### **DATA TRANSFERS**

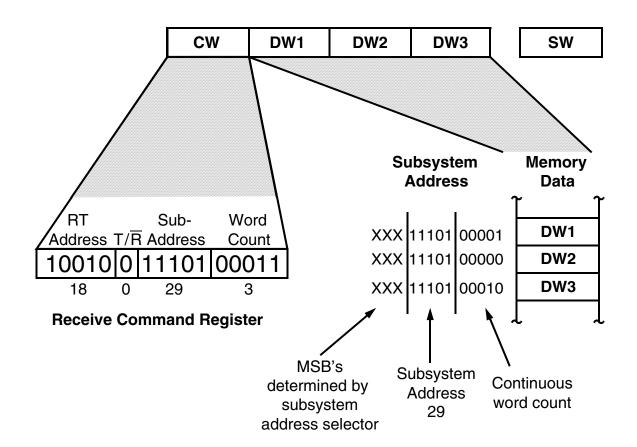

Data transfers in both Bus Controller and Remote Terminal operation are performed via a DMA burst. This powerful feature insures that the host microprocessor system will never be held up more than 16.5 usec when transferring 32 data words into or out of the interface. It also insures that only good and complete messages will be transferred to the host's memory. Operation of the DMA is as follows: When data is received from the 1553 cable via the chip set, it is loaded into an internal FIFO at the 20 µsec/word 1553 rate. Once the complete message has been received and has passed all validity tests, the CT1611 issues the signal DMA REQ to the subsystem. (This signal corresponds to a HOLD request in many systems.) The host microprocessor then acknowledges and grants this request by issuing the signal DMA ACK. The CT1611 then becomes the bus master of the subsystem and transfers all the data on a memory-mapped basis. When the transfer is complete, the CT1611 removes its DMA REQ and returns control of the microprocessor bus to the microprocessor. When data is to be transmitted on the 1553 cable, a similar DMA takes place. Data is preloaded into the FIFO via a single DMA burst and then transmitted.

As a failsafe, an internal timeout is provided to insure that the CT1611 can never control the microprocessor bus longer than 80 µsec. In addition, a hard-wired Master Reset input signal is provided that will place all output signals in a tri-state condition. Therefore, in the unlikely condition of a failure in the CT1611, the host microprocessor system can never be brought down or placed in a non-recoverable state.

A built-in test function has been included to exercise the DMA operation and verify the message data path. This function is initiated by an I/O command from the subsystem.

#### **I/O CONTROL**

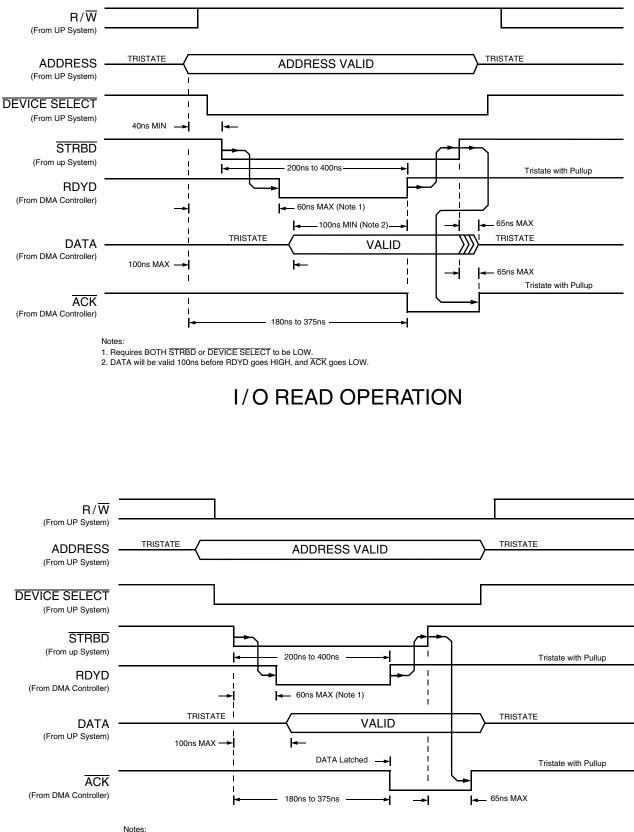

The CT1611 can be addressed, written to, read from, and programmed much like any peripheral device located on a microprocessor bus. The address lines and a device select input signal allow the subsystem to read or write to the CT1611 as if it were memory. In view of the fact that microprocessors are becoming very fast, two types of handshake signals were incorporated into the CT1611, either of which may be used to permit asynchronous read and write operations. Handshaking directly with the 9450A, 8085, 8086 and the 6802 is the active high Ready signal. Handshaking directly with the 68000 or VME and Multibus busses is the active low Acknowledge signal.

#### **INTERFACING**

To accomodate both 8 and 16 bit microprocessor data busses, the CT1611 data path is pin programmable for either operation. When operating in 8 bit mode, data is DMA'd in 8 bit bytes and therefore requires twice the time to be transferred.

Bus control signals are pin programmable for either individual read and write strobes or a common read/write signal and data strobe. Individual read and write strobes are used with the Intel 8085, 8086 and Multibus. A common read/write signal and data strobe are used with the 9450A, 6802, 68000 and VME bus. Two separate pins are provided for input and output data strobes. These signals may be connected or kept separate to insure that 1553 data can never be written into a protected area of memory.

#### **RTU OPERATION**

The CT1611 is powered-up and reset as a Remote Terminal. In addition, in Bus Controller mode, it can be changed into a Remote Terminal via an I/O command.

In Remote Terminal mode, the CT1611 uses dedicated registers for the received command word, the sync data word, and the vector word. The command word register contains a second tier so that receive command words are double buffered. This feature maximizes the allowable I/O access time.

Four interrupts are provided to alert the subsystem that a valid message has been received or transmitted or that a mode command has

SCDCT1611 Rev A

been serviced. Use of the interrupts is optional. The interrupt signals are the same for bus control operation although different in meaning. Interrupts for received or transmitted data messages are generated after the DMA transfers have been completed.

The Busy, Service Request, and Subsystem Error bits for the status word are contained in a dedicated register accessible via I/O. The Busy bit is set high at power-up as well as via a subsystem reset.

#### **BC OPERATION**

The CT1611 is programmable into Bus Controller operation via I/O from the subsystem. Under Bus Controller mode, there are two command word registers, a received mode data register, two returned status word registers, an error latch and a transaction word register.

The first command register is used for all 1553 bus transfers. The second command register is for the second command word used in RT to RT transfers or for the associated mode data required for certain mode codes.

The CT1611 provides full validity checking for all 1553 transfers and alerts the subsystem, via interrupts, as to whether the transfer was valid or not. The two status word registers are preset high at the initiation of a transfer and may be read at completion. The second status word is provided for RT to RT transfers. The error latch may be used to determine the nature of a failure should a transfer be unsuccessful.

The transaction word register is used to define the type of transfer to be performed, to which bus the transfer is to be made, and to define which bits (when set) in the returned status word constitute an invalid transfer.

A polling operation has also been included that enables the CT1611 to automatically load the command words and transaction words from main memory via DMA. This function allows a preprogrammed polling sequence of the remote terminals to be implemented with a minimum of subsystem intervention.

#### **Absolute Maximum Ratings**

| Parameter                           | Range            | Units |

|-------------------------------------|------------------|-------|

| Operating Free-air Temperature      | -55°C to +125    | °C    |

| Storage Case Temperature            | -55°C to +155    | °C    |

| Supply Voltage (VDD)                | -0.3 to +7       | Volts |

| Input and Output Voltage at any Pad | -0.3 to VDD +0.3 | Volts |

#### **Recommended Operating Conditions**

| Parameter             | Min | Тур | Max  | Unit |

|-----------------------|-----|-----|------|------|

| Supply Voltage VDD    | 4.5 | 5.0 | 5.5  | V    |

| Operating Temperature | -55 | -   | +125 | °C   |

#### **Electrical Characteristics**

(VDD = +5.0V  $\pm 10\%$ , TA = -55°C to +125°C, unless otherwise specified)

| Parameter                                 | Conditions | Min | Max  | Unit |

|-------------------------------------------|------------|-----|------|------|

| V <sub>IH</sub> High Level Input Voltage  |            | 2.0 | -    | V    |

| V <sub>IL</sub> Low Level Input Voltage   |            | -   | 0.8  | V    |

| I <sub>IN</sub> Input Current             |            | -10 | +10  | μΑ   |

| I <sub>IL</sub> Low Level Input Current   | Note 4A    | -25 | -400 | μΑ   |

| I <sub>IH</sub> High Level Input Current  | Note 4B    | -25 | -400 | μΑ   |

| V <sub>OH</sub> High Level Output Voltage | Note 1     | 2.4 | -    | V    |

| V <sub>OL</sub> Low Level Output Voltage  | Note 2     | -   | 0.4  | V    |

| I <sub>DD1</sub> Quiescent Supply Current | Note 3     | 5   | 30   | mA   |

| I <sub>DD2</sub> Dynamic Supply Current   | Note 5     | -   | 200  | mA   |

Note 1.  $I_{OH}$  = -2mA for I/O BUS, ADDRESS, R/W & STROBE signal pads (FP and DIP Pins 12->27 / 28->33 / 5,7)

I<sub>OH</sub> = -1mA for OUTPUT ONLY signal pads (FP Pins 1->3,6,9,10,39->42,55->58,65,67->69,79,81->83) (DIP Pins 1->3,6,9,10,39->42,57->60,67,69->71,81,83->85)

Note 2.  $I_{OL} = 4mA$  for I/O BUS, ADDRESS,  $R/\overline{W}$  & STROBE signal pads

(FP and DIP Pins 12->27 / 28->38 / 5,7) IOL = 2mA for OUTPUT ONLY signal pads

(FP Pins 1->3,6,9,10,39->42,55->58,65,67->69,79,81->83) (DIP Pins 1->3,6,9,10,39->42,57->60,67,69->71,81,83->85)

Note 3. Bidirectional I/O at V<sub>DD</sub> (FP Pins 12->27 / 28->38 / 45->52 / 5) (DIP Pins 12->27 / 28->38 / 47->54 / 5)

I/O Address Lines (FP and DIP Pins 34->38) at  $V_{DD}$ , remaining OUTPUTS = N/C, remaining INPUTS at  $V_{DD}$ , MRB at  $V_{IL} < 0.4V$ .

Note 4. For INPUTS

(FP Pins 59,62,63,64,66,77,86) (DIP Pins 61,64,65,66,68,79,88) @ $V_{DD} = 5.5V$ A. @ $V_{IL} = 0.4V$ B. @ $V_{IH} = 2.4V$

Note 5. During typical 32 Word DMA (Output Loading = 0) SCDCT1611 Rev A

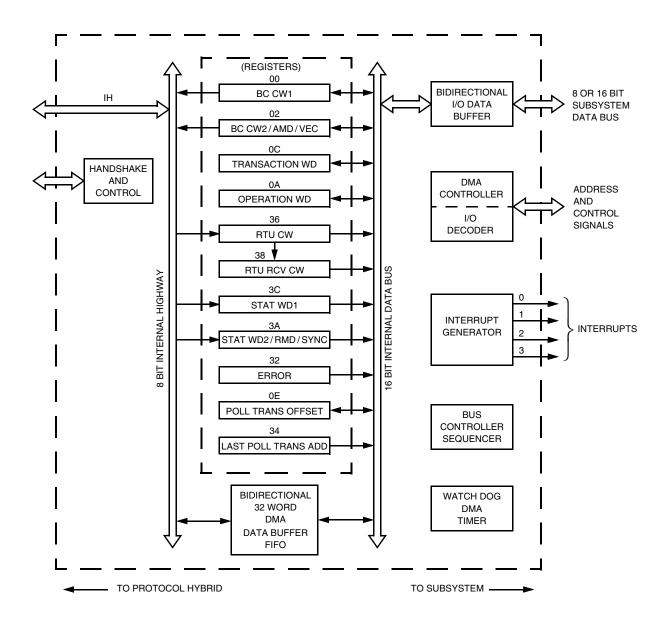

### CT1611 FUNCTIONAL BLOCK DIAGRAM

# CT 1611 User's Guide

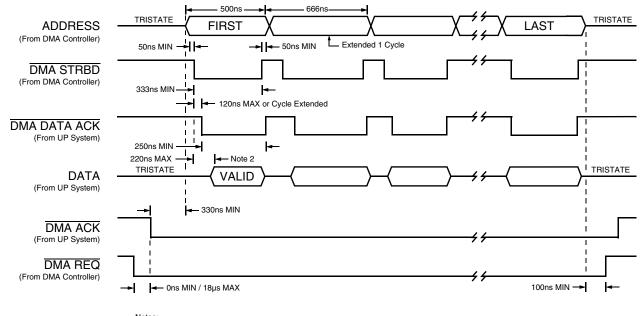

#### **Example of DMA Data Transfer**

Transfer = 3-Word Receive Message in RTU Mode

1. Measured from STRBD or DEVICE SELECT whichever is valid LAST. RDYD requires the coincidence of STRBD and DEVICE SELECT.

#### I/O WRITE OPERATION

Notes:

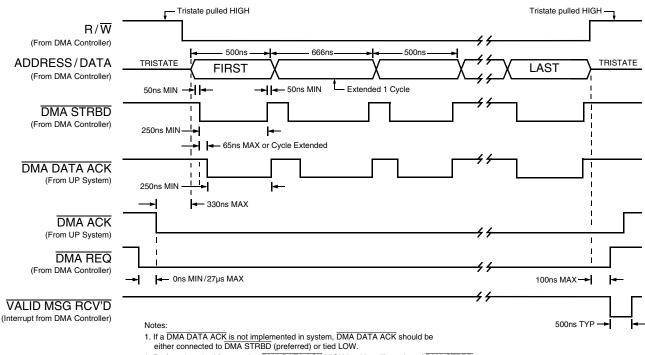

R/W from DMA Controller = Logic "1".

DATA will be valid within 220ns of STRBD or VALID with DMA DATA ACK.

#### DMA READ OPERATION

2. Preferred method for resetting DMA DATA ACK HIGH is with trailing edge of DMA STRBD.

DMA WRITE OPERATION

## Summary of I/O Commands for CT1611 1553B Interface (All Codes HEX)

| Bus Controller  | · I/O                            | Address<br>Code<br>(8 Bit Mode) | Description                                                                                                                                                                |                |                |

|-----------------|----------------------------------|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----------------|

| (Read or Write) | Command Word # 1                 | XX00 (Low)<br>XX01 (High)       | All Transfers                                                                                                                                                              |                |                |

| (Read or Write) | Command Word # 2                 | XX02                            | <ol> <li>Second command word for RT to RT Transfers</li> <li>Also associated mode data for mode change such as sync w/da</li> <li>Also used for RTU vector word</li> </ol> |                | s sync w/data  |

| (Read or Write) | Transaction Word                 | XX0C                            | Defines type of transfer and BUS selection                                                                                                                                 |                |                |

|                 |                                  |                                 | Examples                                                                                                                                                                   |                |                |

|                 |                                  |                                 | Function                                                                                                                                                                   |                | Data           |

|                 |                                  |                                 | Normal xfer<br>Normal xfer                                                                                                                                                 | Bus 0<br>Bus 1 | 0000<br>0008   |

|                 |                                  |                                 | RT to RT                                                                                                                                                                   | Bus 0<br>Bus 1 | 0001<br>0009   |

|                 |                                  |                                 | Mode (No Data)<br>Mode (No Data)                                                                                                                                           | Bus 0<br>Bus 1 | 0003<br>000B   |

|                 |                                  |                                 | Mode (Rtn'd Data), i.e. vector word last cmd, etc.                                                                                                                         | Bus 0<br>Bus 1 | 0005<br>000D   |

|                 |                                  |                                 | Mode (ass'td Data), i.e. sync w/data                                                                                                                                       | Bus 0<br>Bus 1 | 0007<br>000F   |

| (Write Only)    | Trigger                          | XX2A                            | Triggers Bus Transaction<br>Note: Command word(s) and transaction co                                                                                                       | ode must b     | e loaded       |

| (Read Only)     | Status Word 1                    | XX3C                            | Return status word for all transactions (first<br>Note: This register is preset to FFFF at begi<br>at reset.                                                               |                |                |

| BC (Read Only)  | Status Word 2<br>Rtn'd Mode Data | XX3A                            | Second returned status word for RT to RT x<br>Also returned mode data, such as vector wo                                                                                   |                |                |

| RTU (Read Only) | Sync w/Data<br>Sync Word         |                                 |                                                                                                                                                                            |                |                |

| (Read Only)     | Command Word                     | XX36                            | Received command word for all transaction<br>and mode.<br>* use XX38                                                                                                       | is. i.e. tran  | smit, receive* |

| (Read Only)     | Receive Command Word             | XX38                            | Double Buffered version of above for valid receive commands (provides more I/O time).                                                                                      |                | mmands         |

| (Read or Write) | Vector Word                      | XX02                            | Mode Data<br>-to be transmitted<br>- same reg as CW # 2                                                                                                                    |                |                |

## Summary of I/O Commands for CT1611 1553B Interface (All Codes HEX)

| Bus Controller  | : I/O            | Address<br>Code<br>(8 Bit Mode) | Description                                                                                                                                       |

|-----------------|------------------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| (Read Only)     | Sync Word        | XX3A                            | <ol> <li>Mode Data         <ul> <li>to be received</li> </ul> </li> <li>Same as returned mode in BC mode</li> </ol>                               |

| (Write Only)    | Reset I          | XX2E                            | Resets CT1611 interface only                                                                                                                      |

| (Write Only)    | Reset II         | XX2C                            | Resets CT1611 and CT1610 front end, will reset bits in returning status word such as "TF" flag. Same as hard wired master reset used on power up. |

| (Read or Write) | Operational word | XX0A                            | Defines BC mode and RTU mode.<br><u>Data</u> FFF0 = RTU<br>FFF1 = BC<br>Note: Powers up and is reset to busy RTU.                                 |

#### **RTU Mode**

#### 1. Conditions for Busy

When the CT1611 is declared busy, the DMA data transfer operation is inhibited. Mode data is stored in internal registers, and is therefore unaffected by busy. The bust bit is located in the Operation Register.

- 1.1 Busy Set by I/O and POR / RESET

- 1.2 DMA not complete

(This in general should never occur).

- 1.3 FIFO Test

- 1.4 Receive Commands

If a Terminal is declared busy <u>during</u> the reception of a valid message, that message will be received and a DMA request will be generated.

Data will be held indefinately until the DMA request is acknowledged.

Once the DMA is completed, a valid message received interrupt will be generated.

1.5 Transmit Commands

If the subsystem is going to enter a non-interruptable mode and therefore declares itself busy and the condition exists that a transmit command may be received "simultaneously", the subsystem should wait  $6\mu$ sec before beginning. (If a DMA request is not made during this time, none will be made until the terminal is declared not busy).

This insures:

- a. HSFAIL will not occur because of the busy condition missing the command word.

- b. DMA issued, that can't be acknowledged at a "non-interruptable time" by the microprocessor subsystem.

#### Interface Mode

MODE  $1/\overline{\text{MODE 0}}$  — "0" is Motorola/Fairchild 9450 compatibility

"1" is Intel compatibility

| $M1/\overline{M0}$ | Write Operations                                                                                                                                                                                                              | Read Operations                                            |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|

|                    | $\frac{\overline{\text{RDSTB}} / \overline{\text{R}}/\overline{\text{W}} \longrightarrow \overline{\text{R}}/\overline{\text{W}}}{\overline{\text{WTSTB}} / \overline{\text{STRBD}} \longrightarrow \overline{\text{STRBD}}}$ | - Same-                                                    |

| 0                  | $R/\overline{W} = 0$ $\overline{STRBD} = $                                                                                                                                                                                    | $R/\overline{W} = 1$<br>$\overline{STRBD} =$               |

| 1                  | $\frac{\overline{\text{RDSTB}} / \overline{\text{R}} / \overline{\text{W}} \longrightarrow \overline{\text{RDSTB}}}{\overline{\text{WTSTB}} / \overline{\text{STRBD}} \longrightarrow \overline{\text{WTSTB}}}$               | - Same-                                                    |

| 1                  | $\overline{\text{RDSTB}} = 0$ $\overline{\text{WTSTB}} = $                                                                                                                                                                    | $\overline{\text{RDSTB}} = $ $\overline{\text{WTSTB}} = 1$ |

## Operational Commands other than register reads and writes

|                                  | Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Op Code                       | Op Code (DS = 0)                                            |  |

|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-------------------------------------------------------------|--|

| FIFO R<br>Test trig<br>Test trig | Test Triggers - must be in test mode, otherwise no operation results<br>FIFO Reset<br>Test trigger (load)<br>Test trigger (unload)                                                                                                                                                                                                                                                                                                                                   |                               | XX28 <sub>H</sub>                                           |  |

| Operation                        | onal Triggers                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                               |                                                             |  |

| Must be<br>in poll<br>mode       | START POLL (from offset)START POLL (from 0)<br>(resets offset reg.) Reg. Address $000E_H$ CONTINUE POLL (from next address)CONTINUOUS MODE- starts new poll<br>from beginning after "poll op cmplt" INTERRUPTNon-CONTINUOUS- "poll op cmplt" INTERRUPT<br>- then no actionNote: Trigger (does not load new cmd WD (1) or transaction) generally<br>used for non chained poll, single transaction in polling mode. This<br>operation will repeat last, then continue. | X10000X<br>X10001X<br>X10010X | XX20 <sub>H</sub><br>XX22 <sub>H</sub><br>XX24 <sub>H</sub> |  |

| Resets                           | Reset I resets interface only<br>Reset II same as master reset (hardware), also resets chip set                                                                                                                                                                                                                                                                                                                                                                      | X10111X<br>X10110X            | 2E <sub>H</sub><br>2C <sub>H</sub>                          |  |

Note: All Operational Codes are Write Operations.

#### BC Criteria for Valid Transactions

Valid Transactions result in generation of GOOD XFER (INT 0) Interrupt. Invalid Transfer result in generation of INVALID TRANSFER (INT 1) Interrupt. See Transaction Word for additional Status Word Criterion (i.e. bit masks)

| Transaction Type                                                             |                                           | Specific Validity Criteria                                           |

|------------------------------------------------------------------------------|-------------------------------------------|----------------------------------------------------------------------|

| 1. Normal Data Transfer<br>A. RT to BC<br>B. BC to <i>RT</i><br>C. Broadcast | (Tx/Rx = 1)<br>(Tx/Rx = 0)<br>(Tx/Rx = 0) | Status, then Valid Message<br>Status<br>No Status                    |

| 2. RT to RT Transfer<br>A. Normal<br>B. Broadcast                            | (Tx/Rx = 1) $(Tx/Rx = 1)$                 | Status, Valid Message,then Status<br>Status, then Valid Message only |

| 3. Mode (no data)<br>A. Normal<br>B. Broadcast                               |                                           | Status<br>No Status                                                  |

| 4. Mode (associated data)<br>A. Normal<br>B. Broadcast                       |                                           | Status<br>No Status                                                  |

| 5. Mode (returned data)                                                      |                                           | Status, then returned data                                           |

General Validity Criteria - Applies to all transfers

- A. Bus must be quiet, i.e. no additional data words, status words or command words after correct RT response before transaction is declared valid.

- B. If data is returned, word count, must be correct. Data must also be contiguous, i.e. no gaps.

- C. RTU Address(s) must be correct in returned status word(s).

- D. RTU must respond within 14µsec (except for non RT to RT Broadcast).

- E. No bits set in returned status word(s), except where masked in transaction word.

### Interrupts In BC Mode

| BC Interrupt Name       | Signal Name | Conditions and Actions                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Good Transfer           | INT 0       | <ol> <li>Indicates fully valid transaction.</li> <li>Initiates next poll operation, when in polling mode.</li> </ol>                                                                                                                                                                                                                                                                                                                                      |

| Invalid Transfer        | INT 1       | <ol> <li>Non masked bits set (includes reserved bits).</li> <li>No status (2 for non BCST RT to RT) word returned.</li> <li>Status word has incorrect address.</li> <li>Fail safe time out (1 millisec)for bus (RTU) to go quiet i.e.<br/>RTU loudmouthing.</li> <li>Incorrect number of data words.</li> <li>Busy (even if busy masked) when RTU should receive or<br/>transmit data.</li> <li>Note: busy mask only masks busy for mode cmds.</li> </ol> |

| Poll Operation Complete | INT 2       | <ol> <li>Indicates end of poll,when end of poll is a valid transaction.</li> <li><u>Delayed</u> from good transfer interrupt.</li> <li>Initiates poll sequence again (from offset) if in continuous mode.</li> <li>If the I/O command "continue at next transaction" is issued at the last transaction command, this interrupt will be issued.</li> </ol>                                                                                                 |

## Interrupts in RTU Mode

| RTU Interrupt Name     | Signal Name | Conditions and Actions                                                                                                                                                                                                                                                                          |

|------------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Valid Message Received | INT 0       | <ol> <li>Indicates the reception of a complete and valid block of data.</li> <li>Interrupt issued after complete block of data has been DMA'd to<br/>subsystem memory.</li> <li>Command word for receive data block is located in double<br/>buffered receive command register.</li> </ol>      |

| SYNC With Data         | INT 1       | <ol> <li>Issued after reception of valid SYNCHRONIZE with data mode<br/>command. (Interrupt is not generated if word count is high).</li> <li>Command word located in command register.</li> <li>SYNC data word located in SW2/RMD register.</li> </ol>                                         |

| Mode W/O Data          | INT 2       | <ol> <li>Indicates reception of mode commands without data that may<br/>require subsystem action. These are:<br/>SYNCHRONIZE (W/O DATA)<br/>RESET<br/>DYNAMIC BUS CONTROL ACCEPTANCE</li> <li>Command word located in command register.</li> </ol>                                              |

| Data Transmitted       | INT 3       | <ol> <li>Indicates reception of valid transmit command or vector mode<br/>command.</li> <li>If issued for transmit command, then issued after DMA.</li> <li>If issued for vector, data transmitted from CW2/AMD/VEC<br/>register.</li> <li>Command word located in command register.</li> </ol> |

## **Bus Controller Poll Operation**

| Inte   | rnal Triggers                                                                                                                      | Op Code |

|--------|------------------------------------------------------------------------------------------------------------------------------------|---------|

| Trig A | continues operation                                                                                                                | XX24    |

|        | conditions - transaction<br>-poll op enabled<br>-BC mode                                                                           |         |

| Trig B | begin again (from offset)<br>conditions - transaction = last (TB6 = 0)<br>- poll op enable<br>- BC mode<br>- valid trans interrupt | XX20    |

## Summary of Registers

| Register Name                        | General Function                                                                                                                                                                                                                                                                                                                     | Op Code |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| BC Command WD 1 Register             | <ol> <li>Contains the command word for all bus transactions (first for RT to RT transfers).<br/>(BC only)</li> <li>Automatically loaded in polling operation.</li> </ol>                                                                                                                                                             | XX00    |

| CW2/AMD/VEC Register                 | <ol> <li>Used in both RT and BC.</li> <li>Contains second command word for RT to RT transfers. (BC only)</li> <li>Contains associated mode data for mode command requiring transmitted data. (BC only)</li> <li>Optionally automatically loaded in polling operation. (BC only)</li> <li>Contains vector word. (RTU only)</li> </ol> | XX02    |

| Transaction Word Register            | <ol> <li>Contains additional information required to fully define a bus transaction, i.e. bus<br/>selection, transfer type (normal/mode). (BC only)</li> <li>Automatically loaded in polling operation.</li> </ol>                                                                                                                   | XX0C    |

| Transaction Address Register         | 1. Contains starting address for BC polling operation.                                                                                                                                                                                                                                                                               | XX0E    |

| Last Transaction Register            | <ol> <li>Contains address of last transaction.</li> <li>Used to determine where in command stack, a failed transaction command is located.</li> </ol>                                                                                                                                                                                | XX34    |

| Operation Register                   | <ol> <li>Sets operational mode i.e. Bus Controller Remote Terminal</li> <li>Control of status word bits in RTU mode:         <ul> <li>a. BUSY</li> <li>b. SSERR</li> <li>c. SERVRQST</li> </ul> </li> </ol>                                                                                                                          | XX0A    |

| Error Latch                          | <ol> <li>Contains information on transactions occurring on 1553B bus.</li> <li>Primarily used in bus controller mode. Useful in RTU mode especially during system debugging.</li> </ol>                                                                                                                                              | XX32    |

| RTU Command Word Register            | 1. Contains all commands received by RTU. (RTU only). Includes normal data and mode commands.                                                                                                                                                                                                                                        | XX36    |

| RTU Receive Command Word<br>Register | <ol> <li>Contains only valid receive commands. (RTU only)</li> <li>Loaded after data block validated.</li> <li>Doubled buffered version of RTU command word register.</li> </ol>                                                                                                                                                     | XX38    |

| Stat Word 1 Register                 | <ol> <li>Contains returned status word. (BC only).</li> <li>Contains first returned status word for RT to RT transfers. (BC only)</li> </ol>                                                                                                                                                                                         | XX3C    |

| Stat WD2/RMD Register                | <ol> <li>Contains second returned status word for RT to RT transfers. (BC only).</li> <li>Contains returned rode data for mode commands. (BC only). Sync word as RTV.</li> </ol>                                                                                                                                                     | XX3A    |

## **Operation Register**

| MSB<br>15 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | LSB<br>0 |  |

|-----------|----|----|----|----|---|---|---|---|---|---|---|---|---|----------|--|

|           |    |    |    |    |   |   |   |   |   |   |   |   |   |          |  |

1. Power up and reset to busy RTU.

2. Used to define operating mode of 1553 interface, used for both BC and RTU modes

001010

543210 3. Select Code = 00101X

XX0AH  $\overline{\text{DS}} = 0$

| Reg. Bit | Name      | Definition                                                                                                                                                                                                                                           |                                                  |                                        |        |  |  |  |  |

|----------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|----------------------------------------|--------|--|--|--|--|

| 0        | RT/BC     | Terminal Mode<br>0 = RTU Mode<br>1 = BC Mode                                                                                                                                                                                                         |                                                  |                                        |        |  |  |  |  |

| 1        | POE       | Poll Operation Enable<br>Enables Polling Operation in BC Mode<br>0 = Not Enabled<br>1 = Enabled                                                                                                                                                      |                                                  |                                        |        |  |  |  |  |

| 2        | CONT POLL | Continuous Poll Operation Enable causes polling<br>operation to continuously loop when enabled and active.<br>0 = Not Enabled<br>If this bit is reset during an active polling loop, poll will end at<br>completion of polling frame.<br>1 = Enabled |                                                  |                                        |        |  |  |  |  |

| 3        | PFO       | failure. (Invalid Tran<br>Note: Poll can b                                                                                                                                                                                                           | nsfer Interrupt Generat                          | ailed transaction) or next t           |        |  |  |  |  |

| 4,5      | REPEAT    |                                                                                                                                                                                                                                                      | n is detected in BC mo<br>based on the following | de, the interface can RETI<br>g table: | RY the |  |  |  |  |

|          |           | Bit 5                                                                                                                                                                                                                                                | Bit 4                                            | <b>Repeat Count</b>                    |        |  |  |  |  |

|          |           | 0                                                                                                                                                                                                                                                    | 0                                                | None                                   |        |  |  |  |  |

|          |           | 0 1 1                                                                                                                                                                                                                                                |                                                  |                                        |        |  |  |  |  |

|          |           | 1                                                                                                                                                                                                                                                    | 0                                                | 2                                      |        |  |  |  |  |

|          |           | 1 1 3                                                                                                                                                                                                                                                |                                                  |                                        |        |  |  |  |  |

|          |           | The Interface will continue on to the next Transaction if the prescribed number<br>of REPEAT attempts has transpired and the Error condition is still present.                                                                                       |                                                  |                                        |        |  |  |  |  |

## Operation Register con't

| Reg. Bit | Name     | Definition                                                           |                                                         |                                   |                    |  |  |  |  |  |

|----------|----------|----------------------------------------------------------------------|---------------------------------------------------------|-----------------------------------|--------------------|--|--|--|--|--|

| 6,7      | TEST     | FIFO Loop Tests                                                      |                                                         |                                   |                    |  |  |  |  |  |

|          |          | A. 1553 Side Loop<br>NO DMA occur                                    | 'S                                                      |                                   |                    |  |  |  |  |  |

|          |          | B. SUBYSTEM (Mi                                                      |                                                         |                                   |                    |  |  |  |  |  |

|          |          | 1553 Side Set BUSY<br>FIFO Exercised via                             |                                                         |                                   |                    |  |  |  |  |  |

|          |          | I/O Test Trigge<br>an<br>I/O Test Trigge                             |                                                         |                                   |                    |  |  |  |  |  |

|          |          | Bit 7                                                                | Bit 6                                                   | Test                              |                    |  |  |  |  |  |

|          |          | 0                                                                    | 0                                                       | RESET                             |                    |  |  |  |  |  |

|          |          | 1                                                                    | 1                                                       | Test A                            |                    |  |  |  |  |  |

|          |          | 1                                                                    | 0                                                       | Test B                            |                    |  |  |  |  |  |

|          |          | 0                                                                    | 1                                                       | Not Valid                         |                    |  |  |  |  |  |

|          |          | TEST EN                                                              | $\begin{array}{c} & \\ & \\ TEST A \\ ABLE \end{array}$ |                                   |                    |  |  |  |  |  |

| 8        | NO OP    | NO OPERATION (                                                       | Wait) when in poll                                      | mode (BC).                        |                    |  |  |  |  |  |

| 9        | РАСТ     | POLL ACTIVE<br>PACT = 1 indicates                                    | that a POLLING of                                       | peration has been trigg           | gered.             |  |  |  |  |  |

| 10       | DBCACC   | RTU Dynamic Bus 0<br>accept bus control re<br>0 = Not Set<br>1 = Set |                                                         | e when set in RTU Mo<br>PRF-1553B | ode, Rtu will      |  |  |  |  |  |

| 11       | SSERR    | Sets subsystem error                                                 | flag in returned st                                     | atus word (RTU Mode               | e Only).           |  |  |  |  |  |

| 12       | BUSY     | Sets busy bit in retur                                               | med status word, ir                                     | hibits DMA (RTU Mo                | ode only).         |  |  |  |  |  |

| 13       | TRANSACT | TRANSFER ACTIV<br>TRANSACT = 1 inc                                   |                                                         | on has been initiated ar          | nd is in progress. |  |  |  |  |  |

| 14-15    | SERVRQ   | Sets Service Reques                                                  | t in returned status                                    | word (RTU Mode onl                | y).                |  |  |  |  |  |

|          |          | Bit 15 Bit 14 Flag                                                   |                                                         |                                   |                    |  |  |  |  |  |

|          |          | 0 0                                                                  | NOT Set                                                 |                                   |                    |  |  |  |  |  |

|          |          | 0 1 SET until reset                                                  |                                                         |                                   |                    |  |  |  |  |  |

|          |          | 1 0                                                                  | Set until                                               | VECTOR word is tran               | smitted            |  |  |  |  |  |

|          |          | 1 1                                                                  |                                                         |                                   |                    |  |  |  |  |  |

|          |          | * Bit 15 is ALW                                                      | AYS RESET after                                         | VECTOR Word is tra                | nsmitted.          |  |  |  |  |  |

### **Error Register**

| MSE<br>15 | 3<br>14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | LSB<br>0 |  |

|-----------|---------|----|----|----|----|---|---|---|---|---|---|---|---|---|----------|--|

|           |         |    |    |    |    |   |   |   |   |   |   |   |   |   |          |  |

The error Register is reset by: - I/O reg reset command

- I/O reset command

- Power on reset (master reset)

- Initiation of transfer in BC mode

| Bit | Name   | Indication (When Set)                                                                                                                                                                                                                                                                                                           |

|-----|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0*  | RTADER | - RTU address Error (Parity)                                                                                                                                                                                                                                                                                                    |

| 1*  | PARER  | - Parity error in command or data word                                                                                                                                                                                                                                                                                          |

| 2*  | ERROR  | <ul> <li>Any waveform encoding error in received data</li> <li>Bad Manchester</li> <li>Bad Parity</li> <li>Bad Data Sync</li> <li>Non Contiguity of data</li> </ul>                                                                                                                                                             |

| 3*  | LTFAIL | <ul> <li>Encoding error in terminals transmission</li> <li>Includes RT address parity</li> </ul>                                                                                                                                                                                                                                |

| 4   | HSFAIL | - Subsystem has not acknowledged DMA request in sufficient time.                                                                                                                                                                                                                                                                |

| 5   | ТХТО   | <ul> <li>Transmitter timeout error indicates 1553 transmitter has transmitted in excess<br/>of 680µsec and terminal fail safe timeout has turned off transmitter. NOTE:<br/>1553B Max. is 800µs. If terminal timeout hardware (RT) fails self test mode<br/>command (Indicate self test), this bit will also be set.</li> </ul> |

| 6   | DMA TO | - DMA Time Out<br>Indicates failure in data transfer between CT1611 and subsystem. If DMA<br>takes longer than 80μsec this flag will be set and DMA will be initiated.                                                                                                                                                          |

| * Additional information                 |   | Reg. | Bits |   | Indication                           |

|------------------------------------------|---|------|------|---|--------------------------------------|

| for interpretation of Register Bits 0-3. | 3 | 2    | 1    | 0 |                                      |

| Register Dits 0 5.                       | 0 | 1    | 0    | 0 | Waveform encoding error (Manchester) |

|                                          | 0 | 1    | 1    | 0 | Data parity error                    |

|                                          | 1 | Х    | Х    | 1 | RTU address error                    |

| Bit | Name     | Definition                                                                                                                                                                                                   |

|-----|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | DBCACC   | Dynamic Bus Control Acceptance<br>Active only in RTU mode.<br>Indicates RTU has accepted bus controller request.<br>RTU must switch to BC mode.                                                              |

| 8   | TRANS TO | Transaction Time Out<br>Active BC mode only<br>Indicates BC transfer has failed due to loopmouthing RTU or non functioning<br>transceive in BC.<br>Occurs approximately 780µsec after transfer is triggered. |

## Error Register con't

| Bit    | Name        | Indication (WI                                                                                                                                                                                                                                                                                                                                                                                                   | nen Set)                                                                                                                                                               |                                                                    |  |  |  |  |  |  |

|--------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|--|--|--|--|--|--|

| 9      | GBR         | Active BC mode<br>Indicates valid r                                                                                                                                                                                                                                                                                                                                                                              | Good Block Received<br>Active BC mode only<br>Indicates valid message has been received by bus<br>controller, set even if transaction is otherwise<br>not valid.       |                                                                    |  |  |  |  |  |  |

| 10     | RMD         | Active only in E<br>Indicates valid r                                                                                                                                                                                                                                                                                                                                                                            | Received Mode Data<br>Active only in BC mode<br>Indicates valid mode data has been returned from RT.<br>This bit is set even if transaction is otherwise<br>not valid. |                                                                    |  |  |  |  |  |  |

| 11     | BIT SET     | Bit(s) set in returned status word(s). Active in BCC<br>mode only.<br>Indicates non masked bits in status word(s) are set.<br>Masked bits are masked in Transaction Word<br>Register.<br>Bits include:<br>Message error bit<br>Instrumentation bit<br>Service Request<br>Reserved Bit(s) (3 bits)<br>Broadcast Cmd Rcvd bit<br>Busy bit<br>Subsystem Flag<br>Dynamic Bus Control Acceptance bit<br>Terminal Flag |                                                                                                                                                                        |                                                                    |  |  |  |  |  |  |

| 12     | AD ERR      |                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                        | ror active only in BC mode.<br>turned status word(s) is incorrect. |  |  |  |  |  |  |

| 13. 14 | SW CNT      | Returned status<br>Active only in E<br>Two bit non roll                                                                                                                                                                                                                                                                                                                                                          | BC mode.                                                                                                                                                               | r for returned status words                                        |  |  |  |  |  |  |

|        |             | <b>Bit 14</b>                                                                                                                                                                                                                                                                                                                                                                                                    | Bit 13                                                                                                                                                                 | Count                                                              |  |  |  |  |  |  |

|        |             | 0                                                                                                                                                                                                                                                                                                                                                                                                                | 0                                                                                                                                                                      | None returned                                                      |  |  |  |  |  |  |

|        |             | 0                                                                                                                                                                                                                                                                                                                                                                                                                | 1                                                                                                                                                                      | One returned                                                       |  |  |  |  |  |  |

|        |             | 1 0 Two returned                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                        |                                                                    |  |  |  |  |  |  |

|        |             | 1                                                                                                                                                                                                                                                                                                                                                                                                                | 1                                                                                                                                                                      | Three, or greater returned                                         |  |  |  |  |  |  |

| 15     | BUS ACT ERR | Bus Activity Error<br>Active in BC mode only.<br>This bit is set if the bus is active when should be quiet following:<br>A. Returned mode data (indicates word count high)<br>B. After status in normal receive, mode without data, and non broadcast RT<br>to RT.                                                                                                                                               |                                                                                                                                                                        |                                                                    |  |  |  |  |  |  |

#### Transaction Word Register

| MSB<br>15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | LSB<br>0 |  |

|-----------|----|----|----|----|----|---|---|---|---|---|---|---|---|---|----------|--|

|           |    |    |    |    |    |   |   |   |   |   |   |   |   |   |          |  |

Used only in BC mode

Contains information not explicitly contained in command word.

Defines:

- 1. Type of Transfer

- 2. Selection of bus

- selects 1 of 4

- Note: Most systems are only dual redundant

- 3. Continue, for continuous poll operation

- 4. Conditions for defining an invalid transfer via Bit masks for returned status words.

- 5. Continue/last control bit for framing poll operations.

This register is loaded via I/O Command. It is also loaded during a Polling Operation, via DMA from the polling command stack.

| Reg. Bit | Name       | Definitio                                                                         | n                                                   |                                                   |                             |                                                                                                       |                                  |  |

|----------|------------|-----------------------------------------------------------------------------------|-----------------------------------------------------|---------------------------------------------------|-----------------------------|-------------------------------------------------------------------------------------------------------|----------------------------------|--|

| 0 - 2    | TRANS TYPE | Specifies                                                                         | Transactio                                          | on Type                                           |                             |                                                                                                       |                                  |  |

|          |            | Bit 2                                                                             | Bit 1                                               | Bit 0                                             | Transaction                 |                                                                                                       |                                  |  |

|          |            | 0                                                                                 | 0 0 0 NORMAL Receive or Tra                         |                                                   |                             |                                                                                                       |                                  |  |

|          |            | 0                                                                                 | 0                                                   | 1                                                 | RT to                       | RT                                                                                                    |                                  |  |

|          |            | 0                                                                                 | 1                                                   | 0                                                 | No O                        | peration                                                                                              |                                  |  |

|          |            | 0                                                                                 | 1                                                   | 1                                                 | Mode                        | e WITHOUT data                                                                                        |                                  |  |

|          |            | 1                                                                                 | 0                                                   | 0                                                 | No O                        | peration                                                                                              |                                  |  |

|          |            | 1                                                                                 | 0                                                   | 1                                                 | Mode                        | e with RETURNED                                                                                       | data                             |  |

|          |            | 1                                                                                 | 1                                                   | 0                                                 |                             | peration                                                                                              |                                  |  |

|          |            | 1                                                                                 | 1                                                   | 1                                                 | Mode                        | e with associated data                                                                                |                                  |  |

| 3 - 4    | BUS        | Selection                                                                         | of Bus<br>Bit 4                                     | B                                                 | Bit 3                       | Bus                                                                                                   |                                  |  |

|          |            |                                                                                   | 0                                                   |                                                   | 0                           | "0" or "A"                                                                                            |                                  |  |

|          |            |                                                                                   | 0                                                   |                                                   | 1                           | "1" or "B"                                                                                            |                                  |  |

|          |            |                                                                                   | 1                                                   |                                                   | 0                           | "2" or "C"                                                                                            |                                  |  |

|          |            |                                                                                   | 1                                                   |                                                   | 1                           | "3" or "D"                                                                                            |                                  |  |

| 5        | DMA3RD     | For use w<br>When set,<br>transfers)<br>from the c<br>Otherwise<br>transfer.<br>0 | ith RT to 1<br>, during po<br>or the dat<br>command | RT transfe<br>olling sequ<br>a word (fo<br>stack. | ence, the so<br>or mode wit | only)<br>with associated data<br>econd command word<br>h associated data tran<br>mmand/and register v | d (for RT to RT sfers) is loaded |  |

## Transaction Word Register con't

| Reg. Bit | Name      | Definition                                                                                    |                                                                                                                                                                                 |  |  |  |  |  |

|----------|-----------|-----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 6        | POLL CONT | When set polling ope<br>command in comma<br>When Not Set, pollir                              | nue (Polling Mode only)<br>eration will continue with next<br>nd stack.<br>ng operation will terminate after transaction is complete<br>ng sequence must have this bit cleared. |  |  |  |  |  |

| 7 - 15   | MASK BITS | Returned Status Wor<br>1 = Masked<br>0 = Not Masl<br>When a non masked<br>declared not valid. |                                                                                                                                                                                 |  |  |  |  |  |

|          |           | Bit                                                                                           | Status Bit                                                                                                                                                                      |  |  |  |  |  |

|          |           | 7                                                                                             | Terminal Flag                                                                                                                                                                   |  |  |  |  |  |

|          |           | 8                                                                                             | Dynamic Bus Control Acceptance                                                                                                                                                  |  |  |  |  |  |

|          |           | 9                                                                                             | Subsystem Flag                                                                                                                                                                  |  |  |  |  |  |

|          |           | 10                                                                                            | Busy Bit *                                                                                                                                                                      |  |  |  |  |  |

|          |           | 11                                                                                            | Broadcast Command Received                                                                                                                                                      |  |  |  |  |  |

|          |           | 12                                                                                            | Reserved Bits (any or all of 3)                                                                                                                                                 |  |  |  |  |  |

|          |           | 13                                                                                            | Service Request Bit                                                                                                                                                             |  |  |  |  |  |

|          |           | 14                                                                                            | Instrumentation Bit                                                                                                                                                             |  |  |  |  |  |

|          |           | 15 Message Error Bit                                                                          |                                                                                                                                                                                 |  |  |  |  |  |

|          |           | 1 *                                                                                           | Note: Setting the busy bit mask will not mask a busy<br>response (i.e. declare it valid). When data is not<br>returned, in response to a transmit command.                      |  |  |  |  |  |

### CT1611 – Pinouts vs Function

| P  | in # |                    | Р  | in # |                 |

|----|------|--------------------|----|------|-----------------|

| FP | DIP  | Signal             | FP | DIP  | Signal          |

| 1  | 1    | SSERR              | 88 | 90   | +5V             |

| 2  | 2    | TRANSMIT/RECEIVE   | 87 | 89   | BUSY            |

| 3  | 3    | POLL/DATA          | 86 | 88   | BITEN /RMDSTB   |

| 4  | 4    | DS                 | 85 | 87   | LSTCMD /CWEN    |

| 5  | 5    | R/W/RDSTB          | 84 | 86   | HSFAIL          |

| 6  | 6    | RDYD               | 83 | 85   | GBR             |

| 7  | 7    | STRBD /WRSTB (OUT) | 82 | 84   | H/L             |

| 8  | 8    | STRBD /WRSTB (IN)  | 81 | 83   | STATEN /STATSTB |

| 9  | 9    | ACK                | 80 | 82   | RT/BC           |

| 10 | 10   | DMA REQ            | 79 | 81   | DBCACC          |

| 11 | 11   | DMA ACK            | 78 | 80   | TXTO            |

| 12 | 12   | DB 0               | 77 | 79   | SERVREQ         |

| 13 | 13   | DB 1               | 76 | 78   | INCMD           |

| 14 | 14   | DB 2               | 75 | 77   | EOT             |

| 15 | 15   | DB 3               | 74 | 76   | DTRQ            |

| 16 | 16   | DB 4               | 73 | 75   | VECTEN /DWEN    |

| 17 | 17   | DB 5               | 72 | 74   | NBGT            |

| 18 | 18   | DB 6               | 71 | 73   | SYNC            |

| 19 | 19   | DB 7               | 70 | 72   | 16/8            |

| 20 | 20   | DB 8               | 69 | 71   | MODE 1/MODE 0   |

| 21 | 21   | DB 9               | 68 | 70   | IUSTB           |

| 22 | 22   | DB 10              | 67 | 69   | DTACK           |

| 23 | 23   | DB 11              | 66 | 68   | BCOP A          |

| 24 | 24   | DB 12              | 65 | 67   | BCOPSTB         |

| 25 | 25   | DB 13              | 64 | 66   | RTADER          |

| 26 | 26   | DB 14              | 63 | 65   | BCOP B          |

| 27 | 27   | DB 15              | 62 | 64   | PARER           |

| 28 | 28   | AD 0               | 61 | 63   | MANER           |

| 29 | 29   | AD 1               | 60 | 62   | LTFAIL          |

| 30 | 30   | AD 2               | 59 | 61   | DMA DATA ACK    |

| 31 | 31   | AD 3               | 58 | 60   | CLOCK IN (6MHZ) |

| 32 | 32   | AD 4               | 57 | 59   | RTO             |

| 33 | 33   | AD 5               | 56 | 58   | REQBUS B        |

| 34 | 34   | AD 6               | 55 | 57   | REQBUS A        |

| 35 | 35   | AD 7               | 54 | 56   | IHDIR           |

| 36 | 36   | AD 8               | 53 | 55   | ĪHEN            |

| 37 | 37   | AD 9               | 52 | 54   | IH08            |

| 38 | 38   | AD 10              | 51 | 53   | IH19            |

| 39 | 39   | INT 3              | 50 | 52   | IH210           |

| 40 | 40   | INT 1              | 49 | 51   | IH311           |

| 41 | 41   | INT 0              | 48 | 50   | IH412           |

| 42 |      |                    | 47 | 49   | IH513           |

| 43 | 43   | MASTER RESET       | 46 | 48   | IH614           |

| 44 | 44   | COMMON/CASE        | 45 | 47   | IH715           |

| -  | 45   | N/C                | -  | 46   | N/C             |

#### **Ordering Information**

| Model No. | Case      |